JETIR.ORG

ISSN: 2349-5162 | ESTD Year: 2014 | Monthly Issue

# JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

### AN EFFECTIVE STRATEGY FOR AREA-EFFICIENT NANO-AES IMPLEMENTATION FOR INTERNET-OF-THINGS DEVICES

A.SHIVAKRISHNA<sup>1</sup>,Dr.B.NAGESHWAR RAO<sup>2</sup>,Dr.T.VAMSHI<sup>3</sup>

<sup>1</sup>M.Tech Student, Talla Padmavathi College of Engineering, Somidi, Kazipet, Telangana, 506003

<sup>2</sup>Assoc Professor, Talla Padmavathi College of Engineering Student, Somidi, Kazipet, Telangana, 506003

<sup>3</sup>Assoc Professor, Talla Padmavathi College of Engineering, Somidi, Kazipet, Telangana, 506003

<sup>1</sup>shivakrishna25a@gmail.com, <sup>2</sup>nagesh.south@gmail.com, <sup>3</sup>vamshi22g@gmail.com

#### Abstract

Because of the ever-increasing number of tiny internet-connected Things, end-to-end security is critical (IoT). Consequently, cryptography has to be adapted for Internet - Connected devices that have limited resources. Advanced encryption standard (AES) implementation on 65-nm FPGA can help IoT systems with constrained resources, according to this article. Data transmission in the 8-bit format has five main parts. The Key-Register and also the State-Register store all of this information, including the original message, keys, and measurement items. The State Register now uses Shift-Rows to save on paper. Mix-Columns include four internal bits that accept 8-bit data and return 8-bit data in order to adapt to an 8-bit data channel. We built an 8-bit block for this purpose. A single optimized Sub-Byte is shared by the key expansion & encryption processes, making them more efficient. The performance of some Sub-Bytes has been improved by merging and simplifying them. Power consumption is reduced by utilizing the clock gating approach. The performance of application-specific integrated circuits (ASICs) has gone from 35% to 2.4 % in compared to earlier works. For small IoT devices, the proposed design looks to be an adequate cryptosystem.

**Key words**: Advanced encryption standard (AES) algorithm, clock gating, hardware implementation, Internet of Things (IoT), lightweight cryptography.

### 1. Introduction

IoT refers to a huge network of small, interconnected devices that exchange data back to back and forwards between each other. An e-health or transport links systems may profit from this data; these tiny devices might be part of an advanced network that incorporates sensors, communication technologies, and data processing. Security for all sent information in most cases is difficult to achieve as more and more devices are connected. Most end-node tiny devices do not have the resources required to perform cryptography. The creation of lowcost cryptography architectures is an essential research subject because of the rapid growth of the Internet of Things. Cryptographic algorithms that are low on battery power are ideal for rechargeable batteries IoT endnode devices. Many networks, including LoraWan and the Internet - Of - things (IoT), use it as among the most secure symmetrical cryptographic techniques on the market today. There are a variety of levels of security depending on the key length. For IoT applications that require varying levels of security and protocols, the AES encryption with a secure password provides sufficient protection. There are a number of disadvantages to using software to implement AES, including the fact that it takes longer to process data and consumes more power. The use of implementations in rising applications and source of energy devices has increased in recent years. AES implementations for resource-constrained devices have a low throughput with data paths of 8 bits, 16 bits, and 32 bits. Research in this area proposes data path architecture for low-power devices and mobile SoCs. The 8-bit data path has a smaller number of internal wires than the 32-bit data path. Reducing block size is an important goal for us, thus we use low-area design techniques like function merging and block reduction to accomplish this goal. When it comes to key and plain text storage and results, our architecture employs two specialized shift-register memory banks: State and Key. The key expansion & encryption procedures both heavily rely on these two registers. With 65-nm technology, the proposed architecture can be implemented using FPGA and ASIC. ASIC realization of our suggested design based on NIST encryption algorithms is suitable for crypto algorithms in resource limited IoT devices. The hardware implementation looks to be superior to past efforts. Our solution improves chip design area and area—delay products (ADP) by 2.4% for 65-nm technology. However, the precinct with the power rings improves 22.1 percent. Most importantly, we've created a resource-constrained AES architecture for IoT devices. We can achieve this goal by utilizing the following tactics and block designs.

- 1) The State Register incorporates the Shift-Rows to simplify the necessary logic.

- 2) A reduction of 15.5% in area is achieved by optimizing Sub-Bytes blocks and sharing them with the key expansion and encryption phases.

- 3) Since Add-Round-Key follows the structure of 8-bit datapath, we develop an 8-bit block optimized for Mix-Columns with 8-bit input and output based on the structure of the 8-bit datapath. Add-Round Key receives each byte of the results one by one. Key-Register does not need to store results in the registers or increase the datapath to 32-bit in contrast to 32-bit Mix-columns.

- 4) On 65-nm technology, clock gating is used in several portions of the design to lower power usage by 18.9%. It's all laid out in this way for your reading pleasure. It begins with a brief history of the AES algorithm, followed by a discussion of the suggested 8-bit datapath AES architecture and its blocks; implementation results, analysis, and comparison with other similar works; and finally, the project is ended.

### 2. Literature survey

### "AES datapath optimization strategies for low-power low-energy multisecurity level Internet-of-Things applications,"

The absence of security procedures present in currently available Internet of Things (IoT) goods has brought increased focus to the issue of connected devices. Utilizing block cyphers that are both standardised and have been demonstrated to be secure, such as the advanced encryption standard (AES), for the purpose of encrypting data and authenticating users is one way to increase security. On the other hand, the computational power & power/energy consumption required for these security functions might be rather substantial. In this work, we discuss our hardware optimization techniques for AES for high-speed extreme low ultralow-energy Internet of

Things applications with many levels of security. These strategies are optimised for IoT devices that consume very little power and very little energy. Our architecture allows for numerous degrees of security to be implemented by utilising a variety of key sizes, as well as performance / energy optimization for data bus and key expansion. Our implementation may be able to produce an energy per bit equivalent with the lightweight standardised algorithms Présent compared with fewer than 1 pJ/b at 10 MHz at 0.6 V with a throughput of 28 Mb/s using ST FDSOI 28-nm technology, according to the estimated power figures. In terms of the evaluation of the level of security provided by our suggested datapath, a 32-bit key out of 128 bits cannot be deduced by the use of fewer than 20,000 traces in a correlation power analysis assault.

### "Design of AES S-Box using combinational logic optimization"

Strictly speaking, it's a symmetrical encryption algorithm known as the Advanced Encryption Standard. Hardware complexity is dictated by AES permutation (S-box) because it's the only non-linear structure, making it extremely difficult and expensive to implement. Virtex II FPGA chip implements an S-Box combinational logic design for the requested work. By simplifying the logic function's truth table in this way, the architecture aims to reduce time. Basic gate including such AND gates, NOT gate, OR gate, and multiplexer are used in the design of the S-Box. The design theoretically decreases the overall latency and effectively for high-speed applications. In terms of gate area, this approach is appropriate for FPGA implementation. The hardware, the entire area, and the delay are all shown.

## "AES Architectures for Minimum-Energy Operation and Silicon Demonstration in 65nm with Lowest Energy per Encryption"

In order to guarantee sufficient information safety in the upcoming mm systems for the Iot devices, which are expected to deliver a reasonably high throughput while adhering to rigorous area and energy budgets, lightweight cryptographic circuits are an absolute necessity. Because of this, the use of specialised AES accelerators is required, as these offer benefits in terms of energy efficiency that are orders of magnitude greater than those offered by microcontroller-based solutions. In this work, we show the architectural investigation of ultralight AES accelerators with both the intention of reducing the amount of energy that is consumed as much as possible. In lightweight AES designs, the lower value of the number of rounds required for each encryption is expected to be a function of the total number of S-boxes that are at a user's disposal. We provide a low-cost ultraenergy-efficient Aes core for cubic-millimeter platforms, which we combine with sub-/near-threshold circuit approaches. Our test chip has a remarkable energy savings of 0.83 pJ/bit at 0.32V, that is 7 times better than the current state-of-the-art low-cost AES designs.

### 3. Preliminaries

To be more precise, the symmetric cryptography algorithm used by AES contains the following four primary features: Substitute Bytes, Shift Rows, Mix Columns, & Add Round Key. A number of the these functions are executed in the order that is appropriate for each state. For the inputs and its intermediate results, the state consists of 16 bytes organised into four rows of bytes. Accordingly, the number of shots would indeed be 10, 12, & 14 for key lengths 128, 192, & 256 respectively. Every function is carried out one at a time rather than in

the final round, which does not involve the Mix-Columns step. Add-Round-Key is a bitwise XOR operation that is performed between the input and the keys. A circularly left shift through to the row's state is what the AES algorithm refers to as the Shift-Rows operation. The state's secondary, third, & fourth rows are each moved by one, two, & three positions, respectively, according to a cyclical pattern. The state's original row has not been modified in any way. It is referred to as a mix-columns multiplication when two matrices are multiplied together with constant values in each column. Sub-Bytes is a modification that is nonlinear on each and every byte. In order to carry out this function, first the multiplication inverse, also known as MI, is performed, and then an affine transformation, also known as AT, is carried out.

In order to proceed to the next cycle of the algorithm, the original key must first be extended. Each iteration of the procedure requires the utilisation of a key size that is identical to the state's size. XORing, Sub-Byte shifting, and XORing with the a rounded constant are all part of the process of expanding the key (RCON). In the following chapter, we will discuss the operation of AES in great depth.

### 4. Proposed system

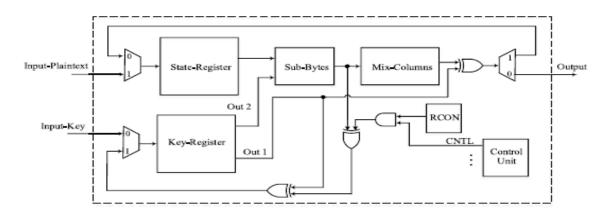

This document provides an explanation of the 8-bit data plane nano-AES architecture that has been proposed. This is the structure we've come up with, as depicted in Figure 1. There seem to be two registers banks called Key-Register & State-Register in the system's design for holding keys and plain text, which also serve as transitory registers for holding intermediate data and an RCON unit and a control unit. An additional purpose of mixing columns and subbytes is to avoid unnecessary procedures.

Fig. 1. Architecture of the proposed nano-AES design.

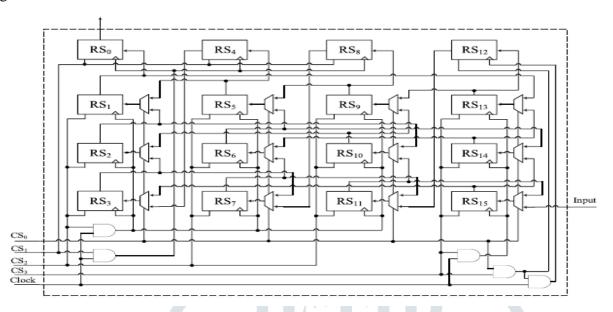

The architecture has two interactions that store intermediate data in register banks all through key expansion & key return. One of the feedback paths is utilised to encrypt the message. The general design of their State-Register concept is shown in Figure 2. The State-Register consists of 16 8-bit memories, each with eight flip-flops. The State-Register gets one 8-bit input as from architecture but one 8-bit outputs if appropriate, using a transition memory structure. In order to save space, Shift-Rows are not constructed as a separate block. It doesn't matter if the input contains Shift-Rows or Sub-Bytes, so they are implemented to each byte. Using Shift-Rows, we were able to get the final results and apply them to the State Register. The State-Shift-Rows Register's function is one of its many responsibilities. Every register of a State-Register requires a multiplexer

to select between two inputs. Data from of the previous register is used to encrypt the data in the current register.

Fig. 2. Structure of the proposed State-Register with Shift-Rows, control circuitry, and clock gating technique.

In the next register, the encrypted data is decoded. To perform Shift-Rows, the multiple State-Register units are linked together in one diagram (Fig. 2) to demonstrate horizontal linkages amongst some of the registers within every row. Wiring causes the rows to be shifted, negating the need for the shift-rows step. The Shift-Row block suggested by Jarvinen et al. needed twelve registers. In order to keep the weight down, a specialised Shift-Rows block requires a lot of area. The cryptosystem's execution requires 150 more clock cycles when using the Shift-Rows incorporated in our suggested State-Register, and the Control-Unit used to activate signals is more complicated. Zhao et al. were the original creators of the Shift-Rows pattern. Found with in Shift-Register of was a 4-1 MUX and three 2-1 MUXs. Our design has twelve 2-1 MUXs. a complex control unit because every MUX and multiple registers have their own control signal. Because of this, the quantity of electricity required increases as the switching factor increases. Shift-Rows and Mix-Columns are permutation operations for rows and columns, respectively. For Mix-Columns to work, a single column of information is necessary. Mix-Columns blocks get data from the State-Register after 4 clock cycles, allowing for the storage and feeding of design data. The findings are returned to the register four clock cycles later. The State-Register provides four control commands that can be used during each process (CS3, CS2, CS1, and CS0). In order to select which registers should be active, the first two CSs (CS1 and CS2) are used. The left side of registers is activated either by AND result between CS0 and CS3, whereas the first column of registers is activated by the CS1 signal. This job has five key responsibilities.

### 5. Discussion on results:

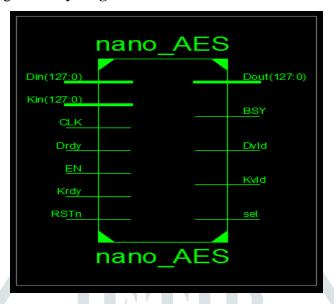

Fig. 3.Entity diagram for nano-AES is shown below

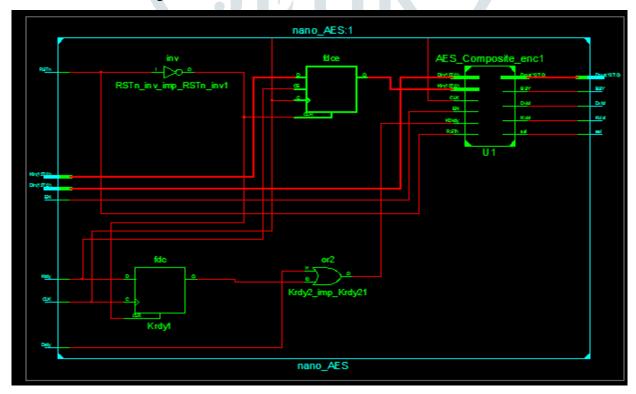

Fig. 4.RTL schematic for nano-AES is shown below

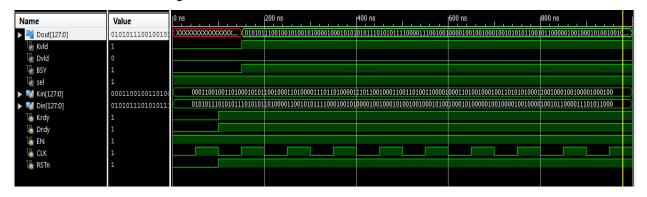

Fig.5.Simulation results are obtained as follows

f907

#### 6. Conclusion

The Iot technology connects ever-increasing numbers of devices (IoT). Overstatement is not an option when discussing the importance of a secure communication system. The small size and resource constraints of Internet of Things (IoT) devices necessitate end-to-end encryption. One of the most secure cryptographic methods is AES, which may be used in a wide range of systems. Small and light IoT devices can use AES because it is a suitable algorithm. We've created a compact AES design for Internet of Things (IoT) devices with minimal resources. It was decided to use an 8-bit datapath using two distinct register banks to store plain text, keys, and intermediate results in the final system design. Logic was reduced by running Shift-Rows somewhere inside the State Register. Sub-Bytes combined with authentication and key expansion reduced the footprint of the design by 15.5% on 65-nm technology. Our mix-Columns design block, which has 8-bit input and output, was also a success. We were able to reduce power usage by 18.9% by implementing the clock gating methodology in numerous different design blocks. In order to verify the design, we put it to the test on the Virtex-5 FPGA. To test and implement the design, 65-nm technology was employed. The chip has a core area of 5448.59 m2 when the power rings are in place. The chip's core has a surface area of 7783.77 m2 without the power rings. In the proposed chip architecture, the area of ADP were both increased by 2.4% and 71.77%, respectively. Over the best identical implementation, the role in the company with both the power rings was enlarged by 22.1 percent Various time periods were used to simulate the design's energy consumption. It was possible to compare our results to those of others there in field by calculating the normalised power in earlier studies. As compared to previous designs, this one required less electricity. According to the findings in the NIST study, the suggested lightweight AES design can be given by low-power hardware and is suitable for resources-constrained systems.. We all know how safe AES is since it is symmetric. 256-bit AES keys remain secure in the age of quantum computing. In the future, we plan to develop a source of energy IoT device AES that is resistant to postquantum attacks. Game performance is greatly affected by these factors. As a remedy to these issues, we'll implement an optimised design architecture.

### 7. References

- [1] N. Sornin, M. Luis, T. Eirich, T. Kramp, And O.Hersent, "Lorawanspecification," Lora Alliance, Tech. Rep., Jan. 2015, Pp. 1–82.[Online]. Available: <a href="https://Loraalliance.Org/ResourceHub/Lorawanrspecification-v10">https://Loraalliance.Org/ResourceHub/Lorawanrspecification-v10</a>

- [2] Z. Liu, K.-K. R. Choo, And J. Großschädl, "Securing Edge Devices In The Post-Quantum Internet Of Things Using Lattice-Based Cryptography," Ieee Commun. Mag., Vol. 56, No. 2, Pp. 158–162, Feb. 2018.

- [3] D.-H. Bui, D. Puschini, S. Bacles-Min, E. Beigné, And X.-T. Tran, "Aes Datapath Optimization Strategies For Low-Power Low-Energy Multisecuritylevel Internet-Of-Things Applications," Ieee Trans. Very Large Scale Integr. (Vlsi) Syst., Vol. 25, No. 12, Pp. 3281–3290, Dec. 2017.

- [4] C. Patrick And P. Schaumont, "The Role Of Energy In The Lightweightcryptographic Profile," In Proc. Nist Lightweight Cryptogr. Workshop, 2016, Pp. 1–16.

- [5] A. Moradi, A. Poschmann, S. Ling, C. Paar, And H. Wang, "Pushing The Limits: A Very Compact And A Threshold Implementation Of Aes," In Proc. Annu. Int. Conf. Theory Appl. Cryptograph. Techn. Tallinn, Estonia: Springer, 2011, Pp. 69–88.

- [6] T. Järvinen, P. Salmela, P. Hämäläinen, And J. Takala, "Efficient Byte Permutation Realizations For Compact Aes Implementations," In Proc.13th Eur. Signal Process. Conf., 2005, Pp. 1–4.

- [7] W. Zhao, Y. Ha, And M. Alioto, "Aes Architectures For Minimum-Energy Operation And Silicon Demonstration In 65 Nm With Lowest Energy Per Encryption," In Proc. Ieee Int. Symp. Circuits Syst. (Iscas), May 2015, Pp. 2349–2352.

- [8] K. Shahbazi, M. Eshghi, And R. Faghih Mirzaee, "Design And Implementation Of An Asip-Based Cryptography Processor For Aes, Idea, And Md5," Eng. Sci. Technol., Int. J., Vol. 20, No. 4, Pp. 1308–1317, Aug. 2017.

- [9] L. Ali, I. Aris, F. S. Hossain, And N. Roy, "Design Of An Ultra High Speed Aes Processor For Next Generation It Security," Comput. Electr. Eng., Vol. 37, No. 6, Pp. 1160–1170, Nov. 2011.

- [10] A. Soltani And S. Sharifian, "An Ultra-High Throughput And Fully Pipelined Implementation Of Aes Algorithm On Fpga," Microprocessors Microsyst., Vol. 39, No. 7, Pp. 480–493, Oct. 2015.

- [11] N. Ahmad, R. Hasan, And W. M. Jubadi, "Design Of Aes S-Box Using Combinational Logic Optimization," In Proc. Ieee Symp. Ind. Electron. Appl. (Isiea), Oct. 2010, Pp. 696–699.

- [12] S. Banik, A. Bogdanov, And F. Regazzoni, "Exploring Energy Efficiency Of Lightweight Block Ciphers," In Proc. Int. Conf. Sel. Areas Cryptogr. Sackville, Nb, Canada: Springer, 2015, Pp. 178–194.

- [13] H. K. Kim And M. H. Sunwoo, "Low Power Aes Using 8-Bit And 32-Bit Datapath Optimization For Small Internet-Of-Things (Iot)," J. Signal Process. Syst., Vol. 91, Nos. 11–12, Pp. 1283–1289, 2019.

- [14] V.-P. Hoang, V.-L. Dao, And C.-K. Pham, "An Ultra-Low Power Aes Encryption Core In 65 Nm Sotb Cmos Process," In Proc. Int. Soc Design Conf. (Isocc), Oct. 2016, Pp. 89–90.

- [15] X. Zhang And K. K. Parhi, "High-Speed Vlsi Architectures For The Aes Algorithm," Ieee Trans. Very Large Scale Integr. (Vlsi) Syst., Vol. 12, No. 9, Pp. 957–967, Sep. 2004.

- [16] C. Paar, "Efficient Vlsi Architectures For Bit-Parallel Computation In Galois Fields," Ph.D. Dissertation, Inst. Dept. Experim. Math., Univ. Duisburg-Essen, Duisburg, Germany, 1994.

- [17] A. Satoh, S. Morioka, K. Takano, And S. Munetoh, "A Compact Rijndael Hardware Architecture With S-Box Optimization," In Proc. Int. Conf.Theory Appl. Cryptol. Inf. Secur. Gold Coast, Qld, Australia: Springer, 2001, Pp. 239–254.

- [18] E. N. Mui, R. Custom, And D. Engineer, "Practical Implementation Of Rijndael S-Box Using Combinational Logic," Custom R&D Engineer Texco Enterprise, Tech. Rep., 2007. [Online]. Available: http://www.Geocities.Ws/Dariuskrail20/Practical\_Implementation\_Of\_Rijndael\_Sbox\_Using\_Combinational\_Logic.Pdf

[19] Federal Information Processing Standards Publication 197, Advanced Encryption Standard Fips Pub 97, 2001, Pp. 1–51.

[20] A. Reyhani-Masoleh, M. Taha, And D. Ashmawy, "New Area Record For The Aes Combined S-Box/Inverse S-Box," In Proc. Ieee 25th Symp. Comput. Arithmetic (Arith), Jun. 2018, Pp. 145–152.